# Control of Grid-Forming Power Converters

Supervisors: Prof. Radu Bojoi Fabio Mandrile Candidate: VALENTINA ZITO

Dipartimento Energia "Galileo Ferraris"

Politecnico di Torino, Italy

15/07/2020

# Outline

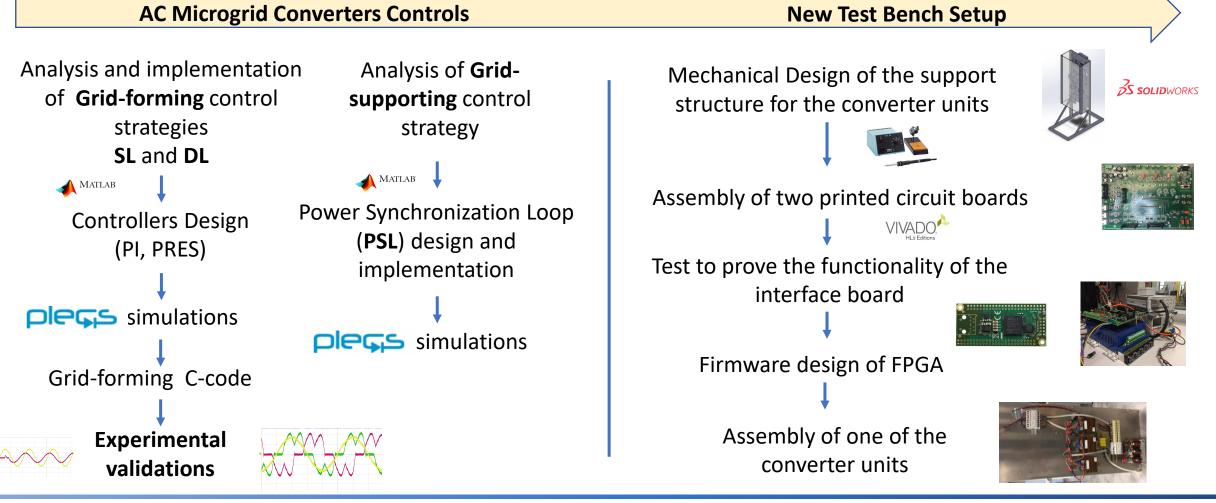

- Introduction

- Controls Analysed

- Simulations

- Experimental Validations

- New Test Bench Setup

- Conclusions

## Introduction

#### **Goal of the Thesis**

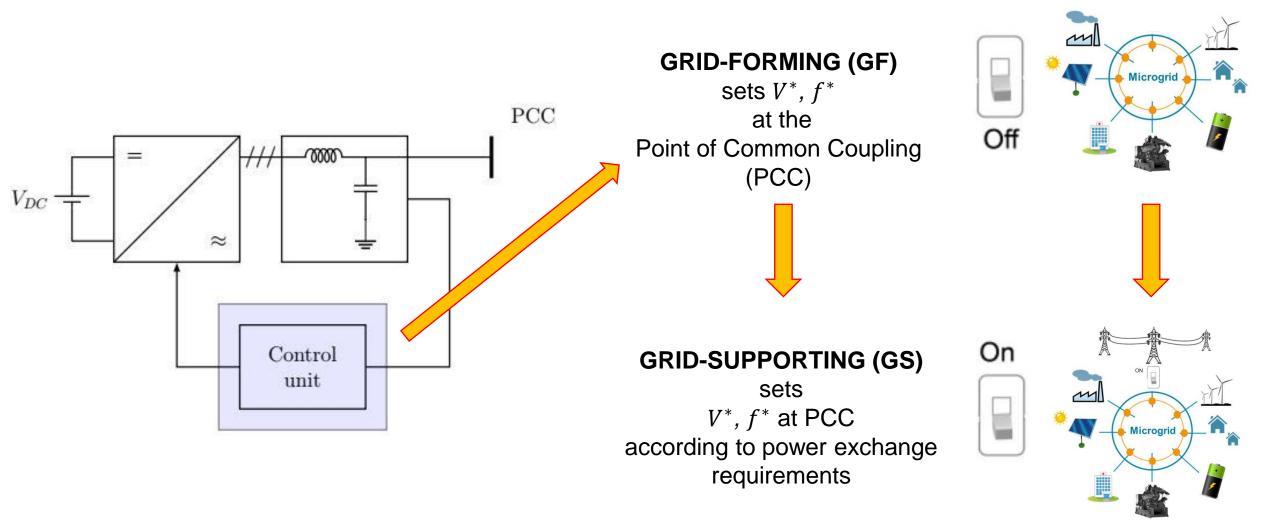

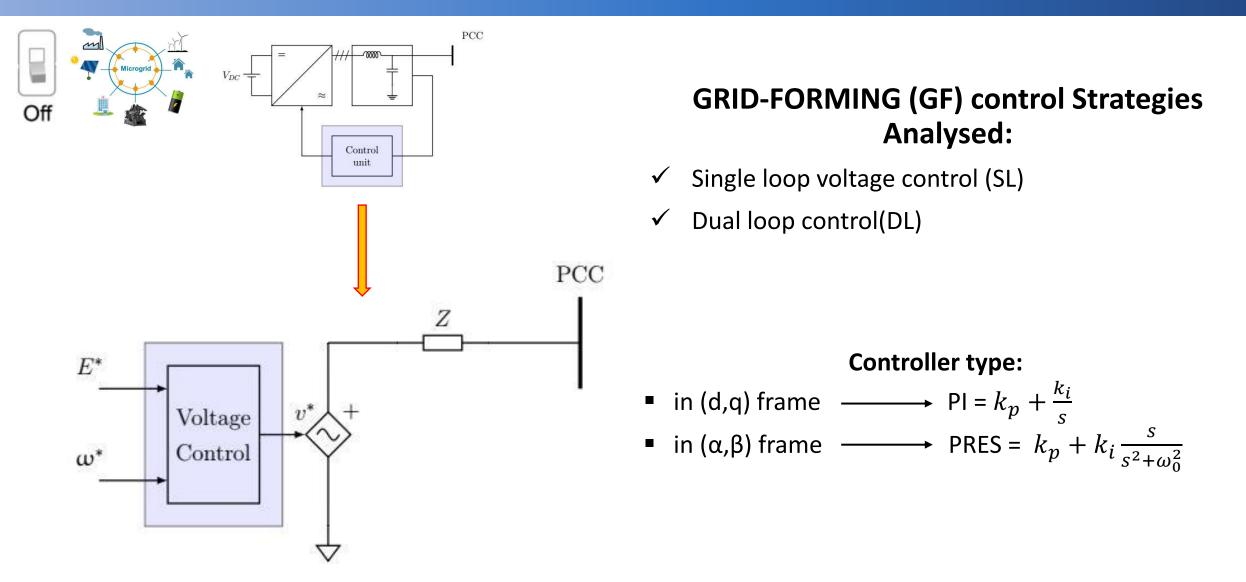

# **Grid-Forming Control Strategy**

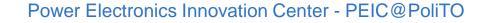

# Single Loop Voltage Control

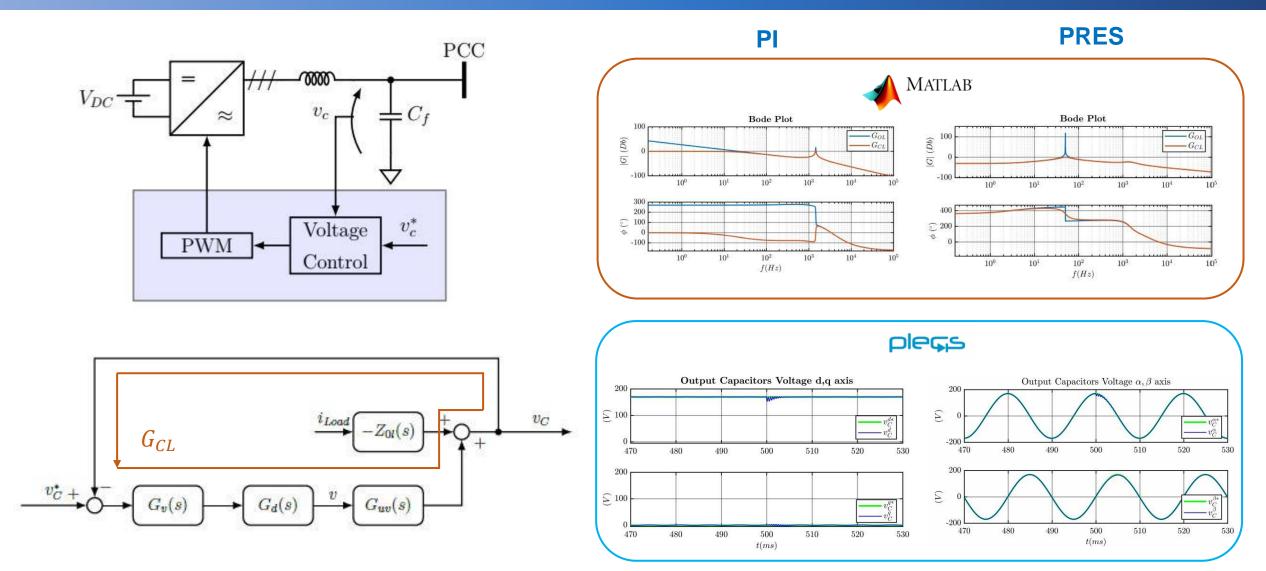

## **Dual Loop Control**

Power Electronics Innovation Center - PEIC@PoliTO

7/18

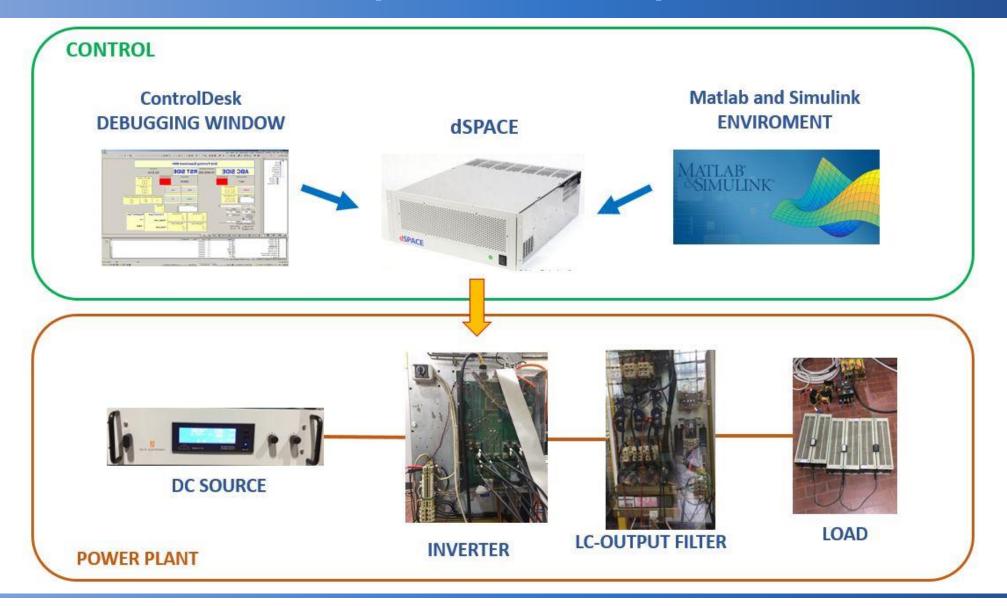

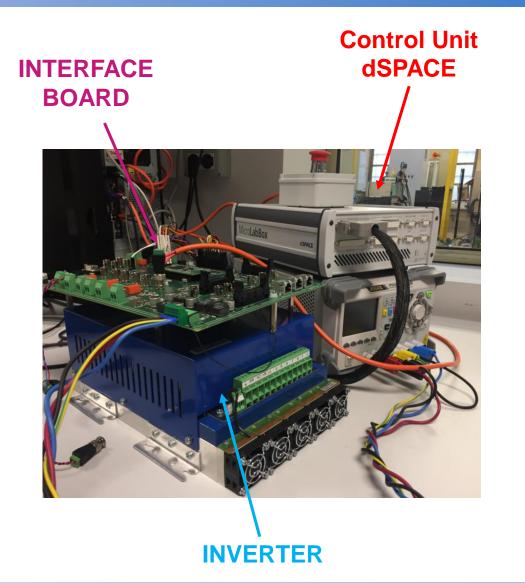

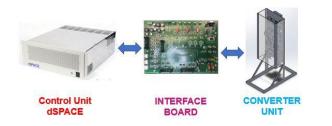

## **Grid-Forming C-code Implementation**

Control Unit dSPACE

#### **Experimental Setup**

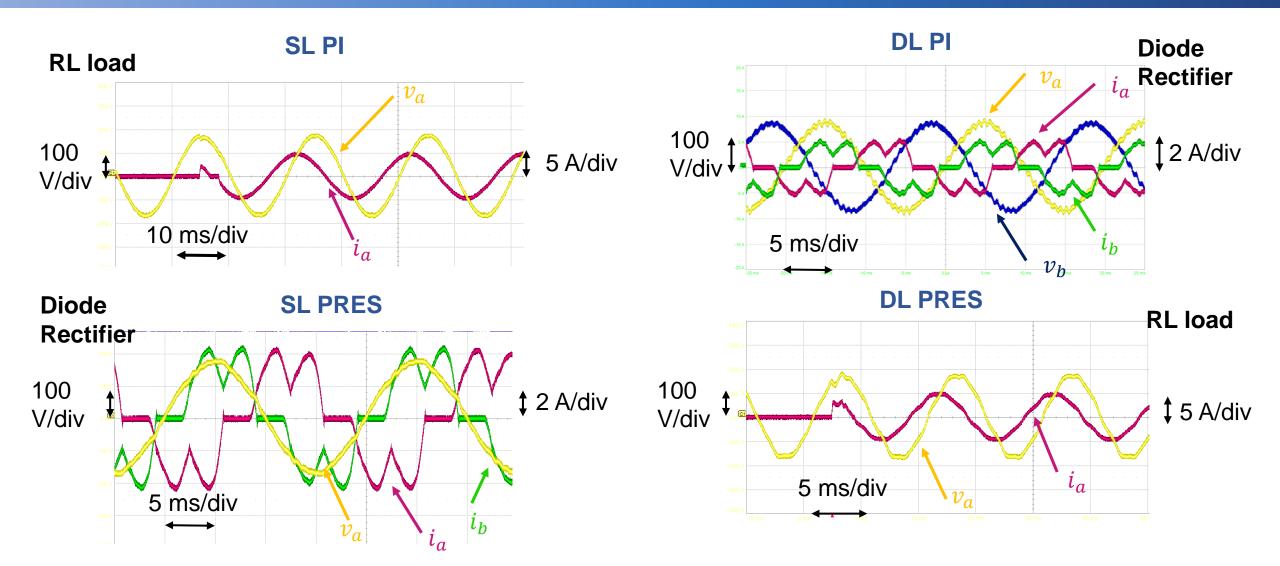

#### **Experimental Results**

# **Grid-Forming: Further Analysis**

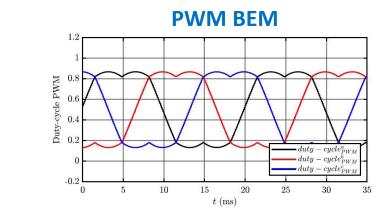

• Two Different Modulation Techniques

1.2

-0.2

0

5

$P_{Switching} = 0.38\%$

THD  $v_{PCC} = 3.70\%$

$P_{Switching} = 0.24\% \sum_{0.6}^{30\%} P_{Switching} = 5.97\%$

**DPWM**

10

15

t (ms)

20

25

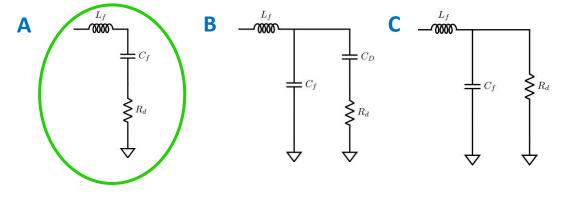

• Damping topologies of LC-output converter filter

(same  $\omega_{LC}$ )  $P_{losses damping Circuit}$ : C > A > B

High frequency attenuation: C > A > B

• Dead Time compensation

|               | IDEAL<br>No Dead-<br>Time added | REAL<br>Dead-Time<br>added | REAL<br>Dead-Time<br>Compensation<br>Algotrithm |

|---------------|---------------------------------|----------------------------|-------------------------------------------------|

| THD $v_{PCC}$ | 3.74%                           | 4.35%                      | 3.90%                                           |

$duty - cycle^b_{DPWA}$

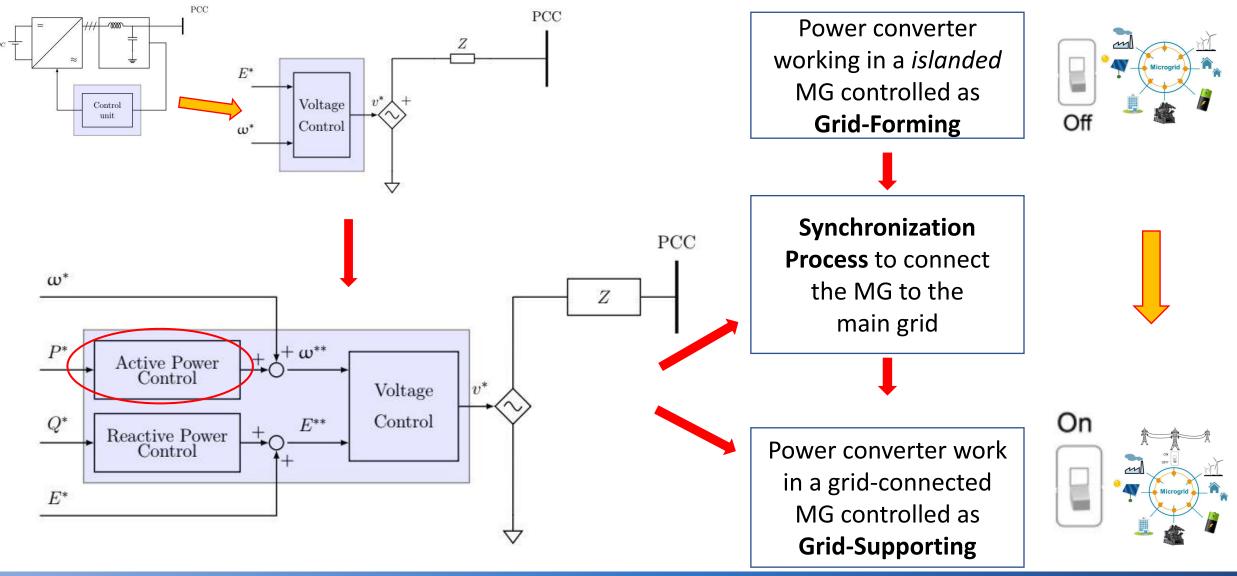

# Grid-Forming → Grid-Supporting

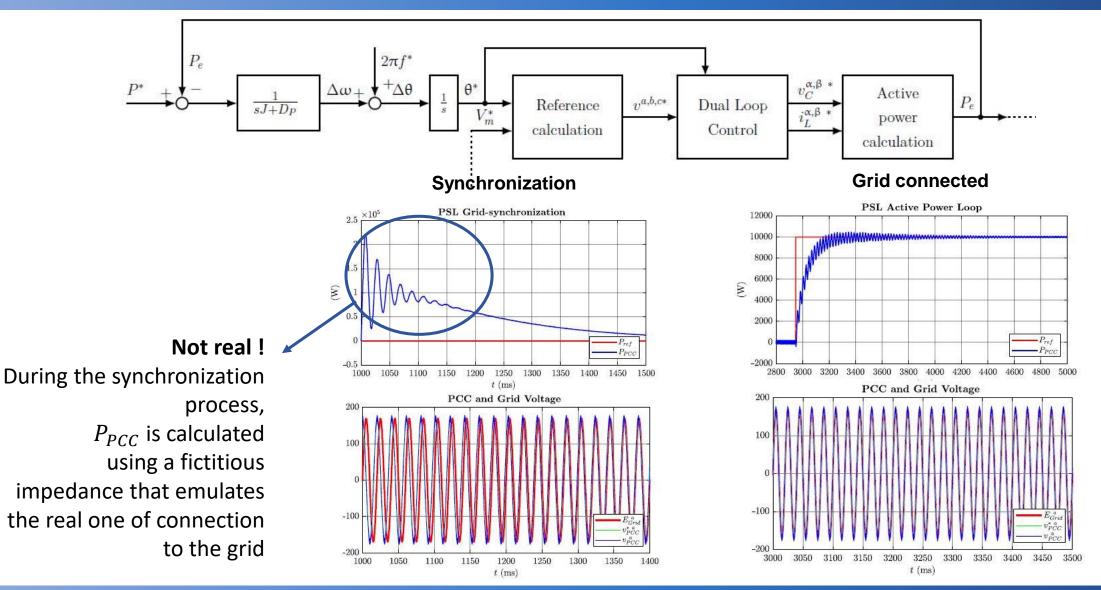

# **Power Synchronization Loop (PSL)**

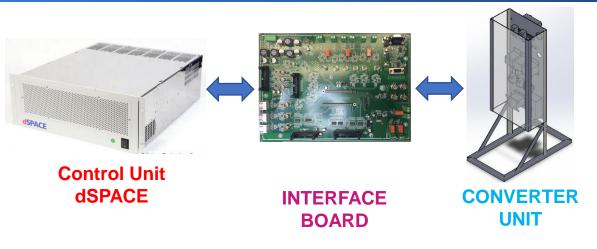

#### **New Test Bench Setup**

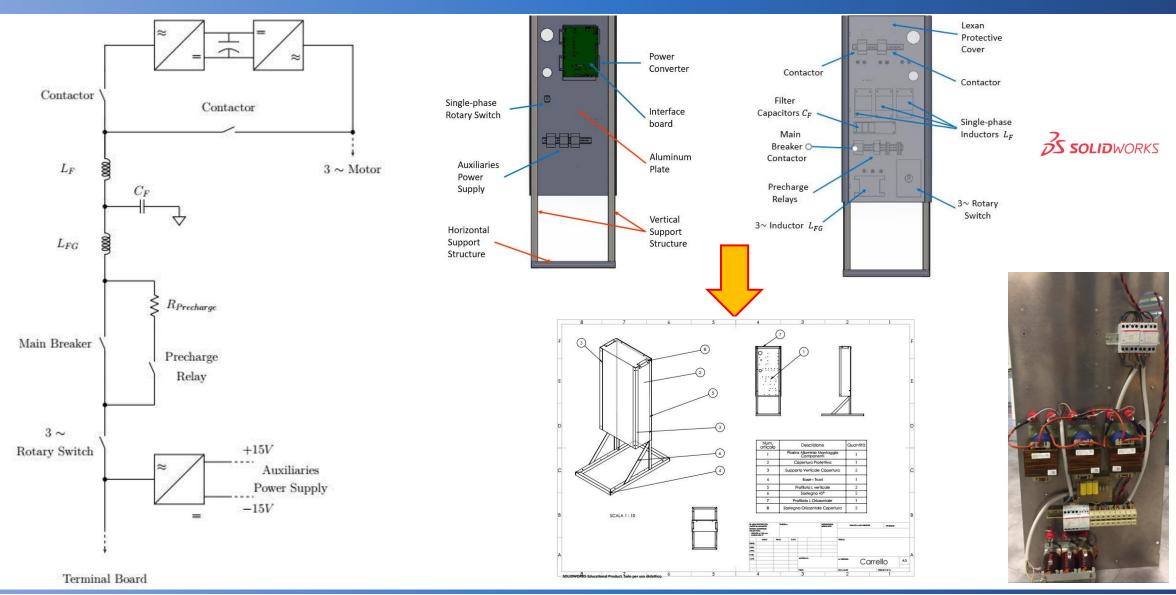

- 1. Mechanical Design of the support structure for the converter units

- 2. Assembly of two printed circuit board

- 3. Test to prove the functionality of the interface board

- 4. Firmware design of FPGA

- 5. Assembly of one of the converter units

## **New Converter Units Support Structure Mechanical Design**

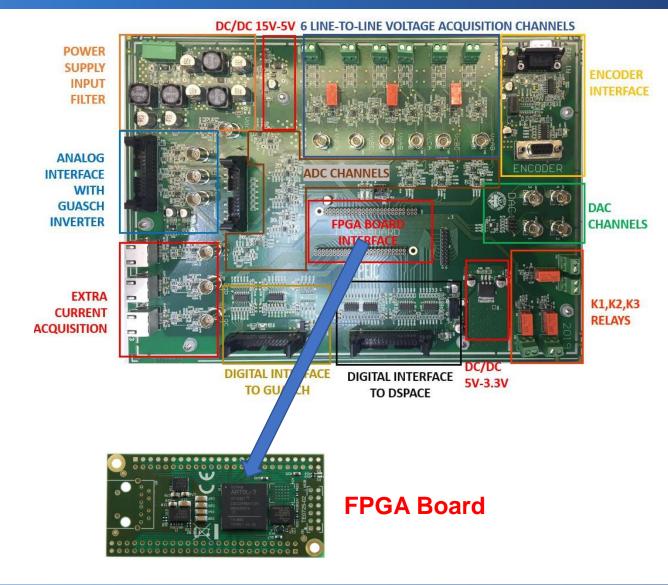

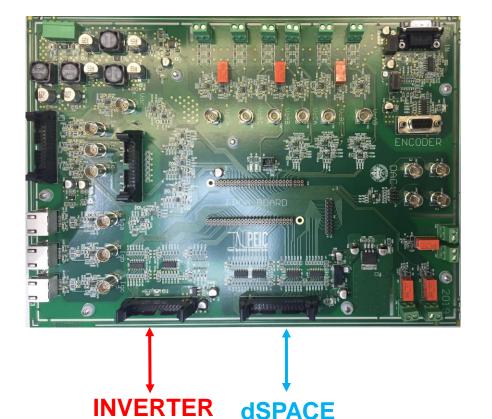

# **Interface Boards Assembly and Preliminary Tests**

#### Preliminary Component Test:

- Power Supply

- Relays

- Leds

- Digital Output Pins

- ADC

•

#### **Interface FPGA Board**

#### **FPGA** tasks:

- Analog acquisitions

- Analog protections

- Driver management

- Communication with dSPACE

- Redirection of the control signals to the power components (Inverter, Relays etc..)

# Conclusions

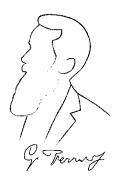

The study of Microgrid Control Strategies is important to ensure their correct functionality.

# Thank you for your attention!